Data sheet

Physical

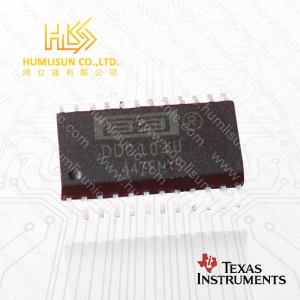

Case/Package

SOIC

Mount

Surface Mount

Number

of Pins

24

Technical

Conversion

Rate

15 kS/s

Dual

Supply Voltage

5

V

Interface

SPI , Serial

Max

Dual Supply Voltage

5.25 V

Max

Operating Temperature

85

°C

Min

Dual Supply Voltage

4.75 V

Min

Operating Temperature

-40 °C

Number

of A/D Converters

1

Number

of Analog Inputs

1

Number

of Bits

20

Number

of Channels

1

Number

of Converters

1

Number

of Elements

1

Polarity

Bipolar , Unipolar

Resolution

20

b

Sampling

Rate

15 kS/s

Supply

Type

Dual , Analog , Digital

Compliance

Lead

Free

Lead Free

Radiation

Hardening

No

RoHS

Compliant

20-BIT ANALOG-TO-DIGITAL CONVERTER

The DDC101 is a precision, wide dynamic range, charge digitizing A/D converter with 20-bit resolution. Lowlevel current output devices, such as photosensors, can bedirectly connected to its input. The most stringent accuracy requirements of many unipolar output sensor applications occur at low signal levels. To meet this requirement, Burr-Brown developed the adaptive delta odulation

architecture of the DDC101 to provide linearly improving noise and linearity errors as the input signal level decreases. The DDC101 combines the functions of current-to-voltage conversion, integration, input programmable gain amplification, A/D conversion, and digital filtering to produce precision, wide dynamic range results. The input signal can be a low level current connected directly into the unit or a voltage connected through a user selected resistor. Although the DDC101 is optimized for unipolar signals, it can also accurately digitize bipolar input signals. The patented delta modulation topology combines charge integration and digitization

functions. Oversampling and digital filtering reduce system noise dramatically. Correlated Double Sampling (CDS) captures and eliminates steady state and conversion cycle dependent offset and switching errors that are not eliminated with conventional analog circuits. The DDC101 block diagram is shown below. During conversion, the input signal is collected on the Internal integration capacitance for a user determined integration period. A high precision, autozeroed comparator samples the analog input node. Tracking logic updates the internal high resolution D/A converter at a 2MHz rate to maintain the analog input at virtual ground. A user programmable digital filter oversamples the tracking logic’s output. The digital filter passes a low noise, high resolution digital output to the serial I/O register. The serial outputs of multiple DDC101 units can be easily connected together

in series or parallel if desired to minimize interconnections.